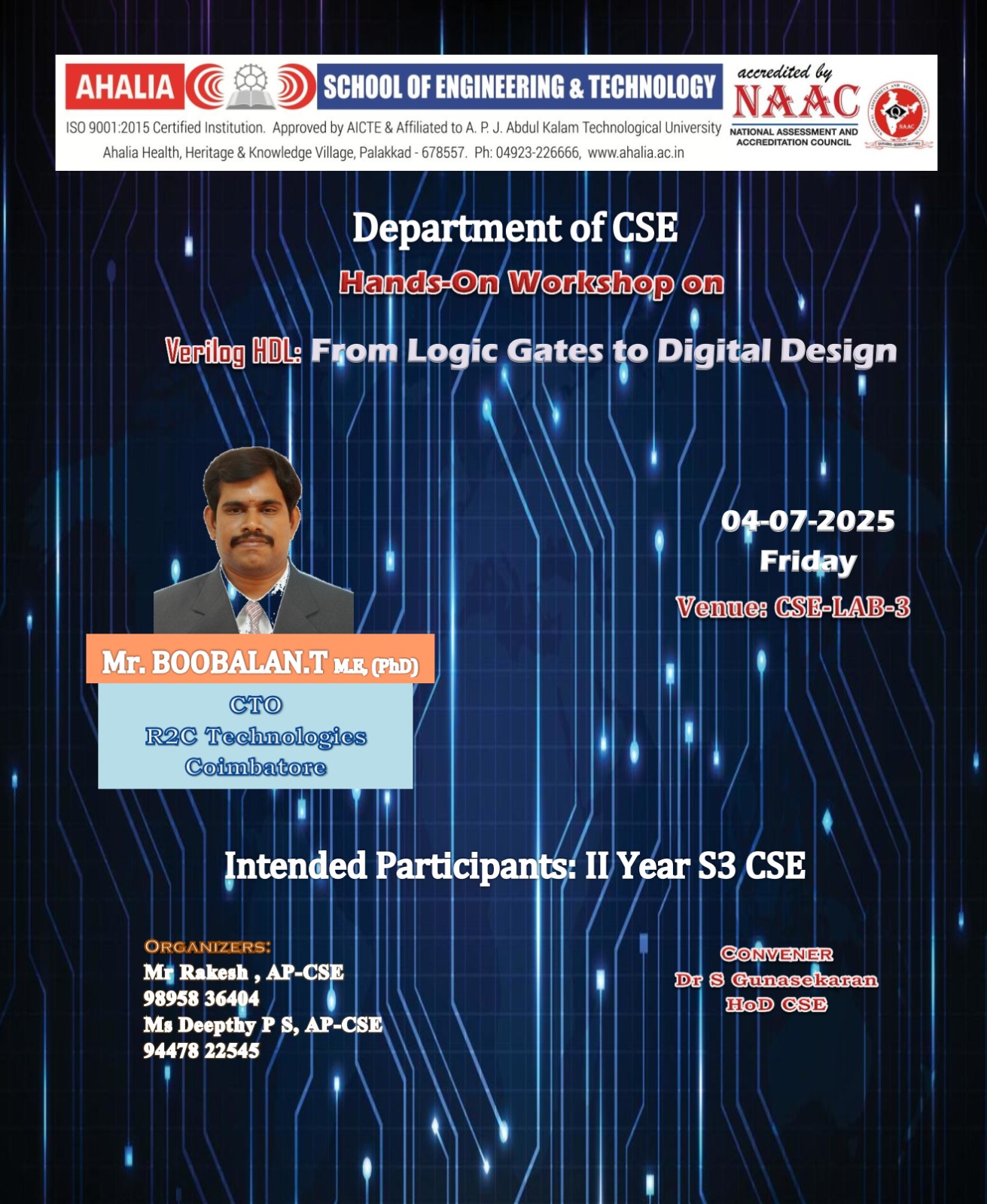

The Department of Computer Science and Engineering organized a workshop titled “Verilog HDL: From Logic Gates to Digital Design” with the objective of bridging the gap between theoretical knowledge and practical implementation in the field of digital system design. The workshop aimed to provide hands-on experience and deeper insights into Verilog HDL (Hardware Description Language), a critical tool for modern digital circuit development and FPGA-based system design. The workshop was conducted by Mr. Boobalan T ME, (PhD), CTO of R2C technologies, Coimbatore.

The Verilog HDL workshop aimed to introduce participants to the fundamentals and importance of Verilog HDL in digital system design. A core objective was to help them understand logic gates and both combinational and sequential circuits using Verilog. Additionally, the workshop focused on providing hands-on experience in coding, simulating, and testing with Verilog. As a result of the workshop, participants gained a strong foundation in Verilog HDL and digital circuit modelling. Students successfully developed and simulated basic logic circuits through Verilog coding. The workshop also successfully sparked interest in advanced topics such as VLSI and embedded systems, with several students expressing interest in pursuing mini-projects using Verilog. The event was graciously coordinated by Dr. Gunasekaran HoD, CSE(Convener), along with Mr. Rakesh (Assistant Professor, CSE) and Deepthy P S (Assistant Professor, CSE) whose meticulous planning ensured the smooth execution of the workshop.